Documentation: Hardware

<< Table of Contents

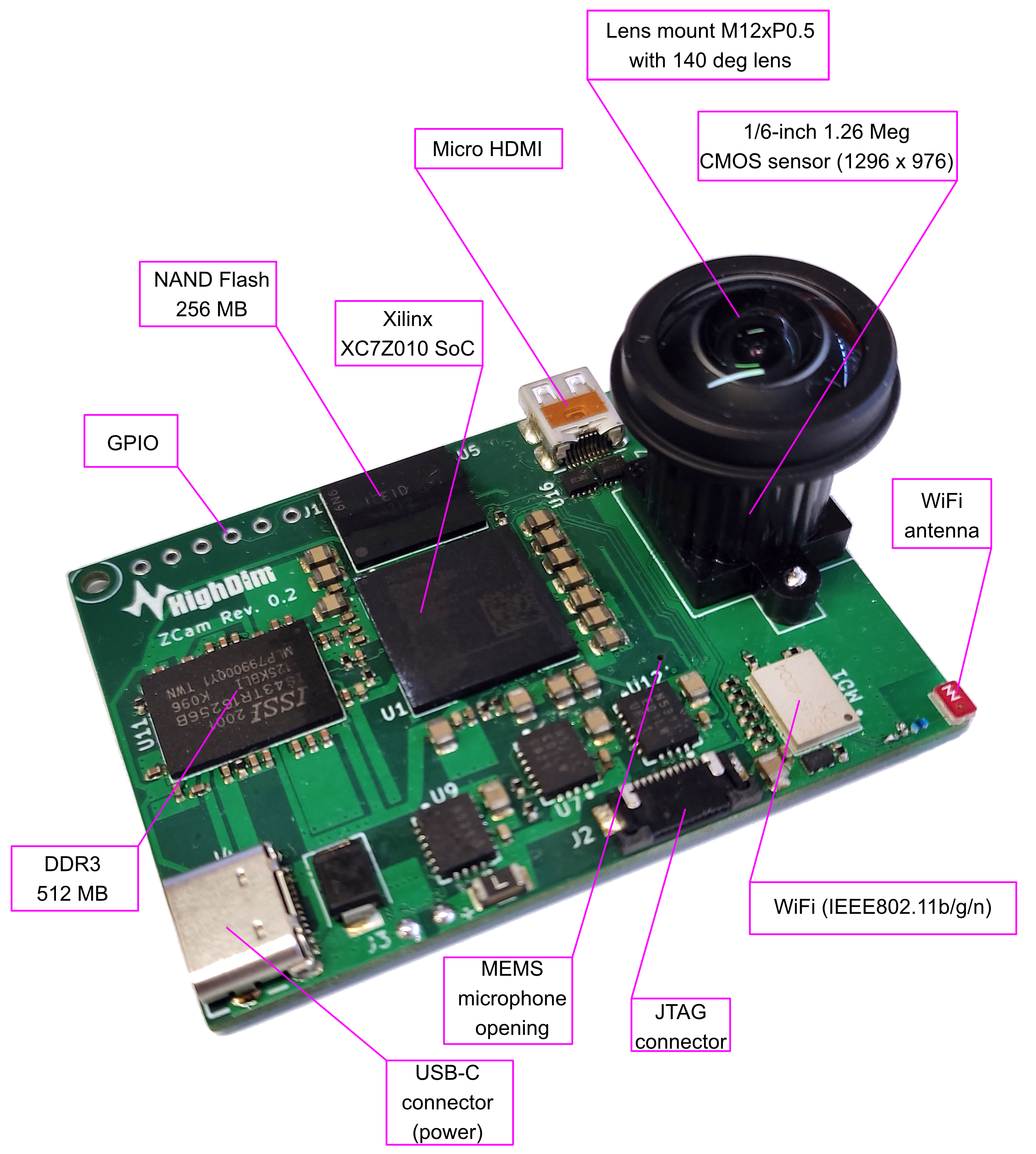

Hardware Overview

Computing system:

- Dual-core ARM + FPGA (Xilinx Zynq XC7Z010-1CLG225C) 666 MHz

- System clock 50 MHz

- DRAM DDR3 512MB 533MHz

- NAND FLASH 256MB 100 MHz

- 1.26 Mp CMOS Image Sensor (MT9M114EBLSTCZ) 1296 x 976 px

- MEMS Microphone (SPH0645LM4H-B)

- WiFi Module (LBEE5KL1DX-883)

- x4 DC/DC, LDO, Reset Supervisor for Zynq

- USB-C for DC power input

- Micro HDMI

- 2.54 mm PIN DC power input

- SFV10R-2STE1HLF (JTAG and UART)

- 2.54 mm 6-pin user GPIO

- M12xP0.5 Lens Mount

- 57 x 41 mm

DC Power Input

DC Power supply is 5V @ 2A

Accepted via USB-C connector or 2.54 mm power pads.

The input power protections:

1. Short-circuit protection: PTC Reset Fuse 6V 2A 2. ESD protection: TVS diode SMBJ5.0A-TR

SoC (FPGA+ARM)

Xilinx Zynq XC7Z010-1CLG225C:

Processor Core: Dual-core ARM Cortex-A9 Max Freq.: 667 MHz (-1) PL: Artix-7 FPGA Logic Cells: 28K LUTs: 17,600 FLIP-FLOPs: 35,200 BRAM: 2.1 Mb (60) DSP: 80 Size: 13 x 13 mm Ball Pitch: 0.8 mmBanks voltages:

BANK500 : 3.3V BANK501 : 1.8V BANK0 : 3.3V BANK34 : 1.8V BANK35 : 3.3VBoot Config:

JTAG: Cascade Mode Boot Mode: NAND PLL: Enabled MIO[0:15] 3.3V MIO[16:53] 1.8V

Debug Connector

Debug 8-pin connector

Connector Pinout:

| Net Name | Conn Pin |

|---|---|

| DBG_TDI | J2:5 |

| DBG_TMS | J2:2 |

| DBG_TDO | J2:3 |

| DBG_TCK | J2:4 |

| ~DBG_RST | J2:1 |

| DBG_PS_TX0 | J2:6 |

| DBG_PS_RX0 | J2:7 |

| GND | J2:8 |

Zynq mapping:

| Pin | Pin Name | Bank | NetName |

|---|---|---|---|

| L7 | TDI_0 | 0 | DBG_TDI |

| L9 | TMS_0 | 0 | DBG_TMS |

| L8 | TDO_0 | 0 | DBG_TDO |

| G9 | TCK_0 | 0 | DBG_TCK |

| B11 | PS_SRST_B_501 | 501 | ~DBG_RST |

| D14 | PS_MIO39_501 | 501 | DBG_PS_TX0 |

| A13 | PS_MIO38_501 | 501 | DBG_PS_RX0 |

User GPIO Connector

2.54 mm 6-pin user connector

Connector pinout:

| Net Name | Conn Pin |

|---|---|

| USER_PS_GPIO0 | J1:4 |

| DONE | J1:5 |

| USER_PS_TX1 | J1:2 |

| USER_PS_RX1 | J1:3 |

| 1V8 | J1:1 |

| GND | J1:6 |

Zynq mapping:

| Pin | Pin Name | Bank | NetName |

|---|---|---|---|

| B12 | PS_MIO48_501 | 501 | USER_PS_GPIO0 |

| A12 | PS_MIO52_501 | 501 | USER_PS_TX1 |

| C13 | PS_MIO53_501 | 501 | USER_PS_RX1 |